Banana Pi BPI-W3 RK3588平台驱动调试篇 [ PCIE篇一 ] - PCIE的开发指南_enable-gpios = <&gpio1 rk_pa4 gpio_active_high>;-程序员宅基地

技术标签: 1024程序员节 Banana pi 开源硬件

RK3588平台驱动调试篇 [ PCIE篇 ] - PCIE的开发指南

1、PCIE接口概述

PCIe(Peripheral Component Interconnect Express)是一种用于连接计算机内部组件的高速接口标准。以下是关于PCIe接口的简要介绍:

- 高速传输: PCIe接口提供了高速的数据传输通道,可用于连接各种硬件设备,如图形卡、存储设备、网络适配器等。它的速度通常以每秒传输的数据位数(例如PCIe x1、x4、x8、x16等)来表示,每个通道的带宽可以根据需要扩展。

- 点对点连接: PCIe采用点对点连接的架构,这意味着每个设备都直接连接到主板上的PCIe插槽,而不需要与其他设备共享带宽。这有助于减少延迟并提高性能。

- 热插拔支持: PCIe接口支持热插拔,允许用户在计算机运行时添加或移除PCIe设备,而不需要重新启动计算机。

- 广泛应用: PCIe接口广泛用于连接图形卡、固态硬盘(SSD)、扩展卡、网络适配器和其他高性能设备。这使得计算机用户可以根据需要扩展和升级系统的性能和功能。

PCIe接口是一种计算机硬件连接标准,它提供了高速、高性能的数据传输通道,支持多种设备的连接。

2、传输速率简介

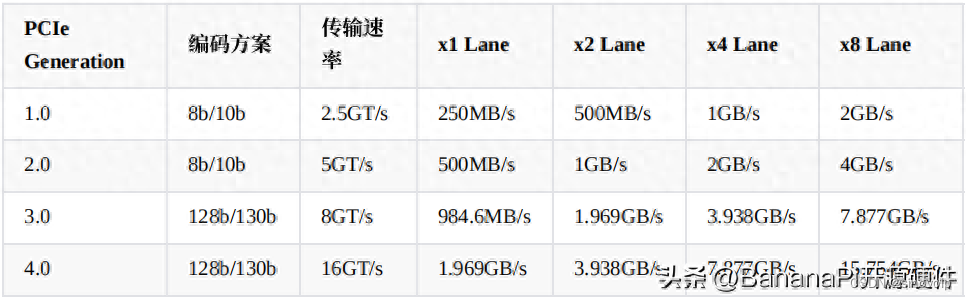

PCIe 分类、速度,按lane的个数分有 x1 x2 x4 x8 x16 (最大可支持32个通道),按代来分 有 gen1 gen2 gen3 gen4

PCIe gen1 和 PCIe gen2 采用的编解码方式是 8b/10b,PCIe gen3 和 之后的 采用的是 128b/130b 的编码方式。

8b/10b 意思是说,当我们要传输8b的数据时,实际在通道上传输的是10b的数据,解码的时候,我们希望得到的是8b的有效数据。这样,相当于有效的带宽是实际带宽的 80%。

同理128b/130b,是传输128bit数据实际线路中传输的是130bit数据。

速率图中的单位间的关系:

传输速率单位 GT/s,表示 千兆传输/秒,是实际每秒传输的位数,他不包括额外吞吐量的开销位。

两个例子:

PCIe gen1 x1 传输速率 2.5GT/s = 2500MT/s = ( 2500 / 10 ) MB/s

PCIe gen3 x1 传输速率 8GT/s = 8000MT/s = ( 8000 / 130 ) x ( 128/8 ) MB/s= 984.6153... MB/s

PCIe 可⽤带宽:吞吐量 = 传输速率 * 编码⽅案

例如:PCIe 2.0 协议的每⼀条 Lane ⽀持58 / 10 = 4 Gbps = 500 MB/s 的速率,Pcie 2.0 x 8的通道为例,x8的可⽤带宽为 48 = 32 Gbps = 4 GB/s。

3、 芯片PCIE资源

3.1 硬件介绍

RK3588共有5个PCIe的控制器,硬件IP是⼀样的,配置不⼀样,其中⼀个4Lane DM模式可以⽀持作为EP使⽤,另外⼀个2Lane和3个1Lane控制器均只能作为RC使⽤。RK3588有两种PCIe PHY,其中⼀种为pcie3.0PHY,含2个Port共4个Lane,另⼀种是pcie2.0的PHY有3个,每个都是2.0 1Lane,跟SATA和USB combo使⽤。pcie3.0 PHY的4Lane可以根据实际需求拆分使⽤,拆分后需要合理配置对应的控制器。

3.2 kernel dts解析之PCIe

控制器在DTS对应节点名称:

| 资源 |

模式 |

dts节点 |

可用phy |

内部DMA |

| PCIe |

RC/EP |

pcie3x4: |

pcie30phy |

是 |

| PCIe |

RC only |

pcie3x2: |

pcie30phy |

否 |

| PCIe |

RC only |

pcie2x1l0: |

pcie30phy, |

否 |

| PCIe |

RC only |

pcie2x1l1: |

pcie30phy, |

否 |

| PCIe |

RC only |

pcie2x1l2: |

combphy0_ps |

否 |

在kernel/arch/arm64/boot/dts/rockchip/rk3588.dtsi下有具体描述

使用限制

- pcie30phy拆分后,pcie30x4控制器,⼯作于2Lane模式时只能固定配合pcie30phy的port0,⼯作于 1Lane模式时,只能固定配合pcie30phy的port0lane0;

- pcie30phy拆分后,pcie30x2控制器,⼯作于2Lane模式时只能固定配合pcie30phy的port1,⼯作于 1Lane模式时,只能固定配合pcie30phy的port1lane0;

- pcie30phy拆分为4个1Lane,pcie3phy的port0lane1只能固定配合pcie2x1l0控制器,pcie3phy的 port1lane1只能固定配合pcie2x1l1控制器;

- pcie30x4控制器⼯作于EP模式,可以使⽤4Lane模式,或者2Lane模式使⽤pcie30phy的port0, pcie30phy的port1中2lane可以作为RC配合其他控制器使⽤。默认使⽤common clock作为reference clock时,⽆法实现pcie30phy port0的lane0⼯作于EP模式,lane1⼯作于RC模式配合其他控制器使 ⽤,因为Port0的两个lane是共⽤⼀个输⼊的reference clock,RC和EP同时使⽤clock可能会有冲突。

- RK3588 pcie30phy 如果只使⽤其中⼀个port,另⼀个port也需要供电,refclk等其他信号可接地。

4、PCIe 使用配置

4.1 简介

Armsom-W3开发板上有 1 个 PCIe3.0 x 4 接口和一个PCIe2.0接口,如图

可以插入对应模组使用, 如图:

4.2 硬件设计

PCIe3.0 x 4 接口:

PCIe 2.0接口:

PCIe 2.0接口:

4.3 软件配置

一般根据原理图在 DTS 中配置供电引脚、复位引脚,选择正确的 pcie 控制器节点和 PHY 节点使能就可以。

在kernel/arch/arm64/boot/dts/rockchip/rk3588-armsom-w3.dts中配置如下:

/ {

vcc12v_dcin: vcc12v-dcin {

compatible = "regulator-fixed";

regulator-name = "vcc12v_dcin";

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = <12000000>;

regulator-max-microvolt = <12000000>;

};

vcc5v0_sys: vcc5v0-sys {

compatible = "regulator-fixed";

regulator-name = "vcc5v0_sys";

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

vin-supply = <&vcc12v_dcin>;

};

vcc3v3_pcie2x1l0: vcc3v3-pcie2x1l0 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie2x1l0";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

regulator-boot-on;

regulator-always-on;

gpios = <&gpio1 RK_PD2 GPIO_ACTIVE_HIGH>;

startup-delay-us = <50000>;

vin-supply = <&vcc5v0_sys>;

};

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpios = <&gpio1 RK_PA4 GPIO_ACTIVE_HIGH>;

startup-delay-us = <5000>;

vin-supply = <&vcc5v0_sys>;

};

}

&pcie2x1l0 {

reset-gpios = <&gpio4 RK_PA5 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie2x1l0>;

status = "okay";

};

&combphy1_ps {

status = "okay";

};

&pcie30phy {

rockchip,pcie30-phymode = <PHY_MODE_PCIE_AGGREGATION>;

status = "okay";

};

&pcie3x4 {

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

pcie30phy、combphy1_ps:PHY 节点

pcie3x4、pcie2x1l0:pcie3x4 控制器节点

reset-gpios:复位引脚属性

vcc3v3_pcie2x1l0、vcc3v3_pcie30:供电引脚节点

4.4 其他PCIE配置的实例

RK3588的控制器和PHY较多,按配置要点进⾏配置即可,这⾥还有⼏个典型范例供参考:

4.4.1 ⽰例1 pcie3.0phy拆分2个2Lane RC, 3个PCIe 2.0 1Lane

/ {

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpios = <&gpio3 RK_PC3 GPIO_ACTIVE_HIGH>;

startup-delay-us = <5000>;

vin-supply = <&vcc12v_dcin>;

};

};

&combphy0_ps {

status = "okay";

};

&combphy1_ps {

status = "okay";

};

&combphy2_psu {

status = "okay";

};

&pcie2x1l0 {

phys = <&combphy1_ps PHY_TYPE_PCIE>;

reset-gpios = <&gpio4 RK_PA5 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie2x1l1 {

phys = <&combphy2_psu PHY_TYPE_PCIE>;

reset-gpios = <&gpio4 RK_PA2 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie2x1l2 {

reset-gpios = <&gpio4 RK_PC1 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie30phy {

/*pcie30phy的组合使⽤模式:

PHY_MODE_PCIE_NANBNB /* P1:PCIe3x2 + P0:PCIe3x2 */

PHY_MODE_PCIE_NANBBI /* P1:PCIe3x2 + P0:PCIe3x1*2 */

PHY_MODE_PCIE_NABINB /* P1:PCIe3x1*2 + P0:PCIe3x2 */

PHY_MODE_PCIE_NABIBI /* P1:PCIe3x1*2 + P0:PCIe3x1*2 */

*/

rockchip,pcie30-phymode = <PHY_MODE_PCIE_NANBNB>;

status = "okay";

};

&pcie3x2 {

reset-gpios = <&gpio4 RK_PB0 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie3x4 {

num-lanes = <2>;//拆分为2lan使用

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

4.4.2 ⽰例2 pcie3.0phy拆分为4个1Lane, 1个使⽤PCIe 2.0 1 Lane

/ {

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpios = <&gpio3 RK_PC3 GPIO_ACTIVE_HIGH>;

startup-delay-us = <5000>;

vin-supply = <&vcc12v_dcin>;

};

};

&combphy0_ps {

status = "okay";

};

&pcie2x1l0 {

phys = <&pcie30phy>;

reset-gpios = <&gpio4 RK_PA5 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie2x1l1 {

phys = <&pcie30phy>;

reset-gpios = <&gpio4 RK_PA2 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie2x1l2 {

reset-gpios = <&gpio4 RK_PC1 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie30phy {

rockchip,pcie30-phymode = <PHY_MODE_PCIE_NABIBI>;

status = "okay";

};

&pcie3x2 {

num-lanes = <1>;

reset-gpios = <&gpio4 RK_PB0 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie3x4 {

num-lanes = <1>;

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

pcie30phy拆分为4个1Lane时,port0lane0固定配合pcie3x4控制器,pcie3phy的port0lane1固定配合pcie2x1l0控制器,port1lane0固定配合pcie3x2控制器,pcie3phy的port1lane1固定配合pcie2x1l1控制器,加上combphy0_ps固定配合pcie2x1l2。

智能推荐

5个超厉害的资源搜索网站,每一款都可以让你的资源满满!_最全资源搜索引擎-程序员宅基地

文章浏览阅读1.6w次,点赞8次,收藏41次。生活中我们无时不刻不都要在网站搜索资源,但就是缺少一个趁手的资源搜索网站,如果有一个比较好的资源搜索网站可以帮助我们节省一大半时间!今天小编在这里为大家分享5款超厉害的资源搜索网站,每一款都可以让你的资源丰富精彩!网盘传奇一款最有效的网盘资源搜索网站你还在为找网站里面的资源而烦恼找不到什么合适的工具而烦恼吗?这款网站传奇网站汇聚了4853w个资源,并且它每一天都会持续更新资源;..._最全资源搜索引擎

Book类的设计(Java)_6-1 book类的设计java-程序员宅基地

文章浏览阅读4.5k次,点赞5次,收藏18次。阅读测试程序,设计一个Book类。函数接口定义:class Book{}该类有 四个私有属性 分别是 书籍名称、 价格、 作者、 出版年份,以及相应的set 与get方法;该类有一个含有四个参数的构造方法,这四个参数依次是 书籍名称、 价格、 作者、 出版年份 。裁判测试程序样例:import java.util.*;public class Main { public static void main(String[] args) { List <Book>_6-1 book类的设计java

基于微信小程序的校园导航小程序设计与实现_校园导航微信小程序系统的设计与实现-程序员宅基地

文章浏览阅读613次,点赞28次,收藏27次。相比于以前的传统手工管理方式,智能化的管理方式可以大幅降低学校的运营人员成本,实现了校园导航的标准化、制度化、程序化的管理,有效地防止了校园导航的随意管理,提高了信息的处理速度和精确度,能够及时、准确地查询和修正建筑速看等信息。课题主要采用微信小程序、SpringBoot架构技术,前端以小程序页面呈现给学生,结合后台java语言使页面更加完善,后台使用MySQL数据库进行数据存储。微信小程序主要包括学生信息、校园简介、建筑速看、系统信息等功能,从而实现智能化的管理方式,提高工作效率。

有状态和无状态登录

传统上用户登陆状态会以 Session 的形式保存在服务器上,而 Session ID 则保存在前端的 Cookie 中;而使用 JWT 以后,用户的认证信息将会以 Token 的形式保存在前端,服务器不需要保存任何的用户状态,这也就是为什么 JWT 被称为无状态登陆的原因,无状态登陆最大的优势就是完美支持分布式部署,可以使用一个 Token 发送给不同的服务器,而所有的服务器都会返回同样的结果。有状态和无状态最大的区别就是服务端会不会保存客户端的信息。

九大角度全方位对比Android、iOS开发_ios 开发角度-程序员宅基地

文章浏览阅读784次。发表于10小时前| 2674次阅读| 来源TechCrunch| 19 条评论| 作者Jon EvansiOSAndroid应用开发产品编程语言JavaObjective-C摘要:即便Android市场份额已经超过80%,对于开发者来说,使用哪一个平台做开发仍然很难选择。本文从开发环境、配置、UX设计、语言、API、网络、分享、碎片化、发布等九个方面把Android和iOS_ios 开发角度

搜索引擎的发展历史

搜索引擎的发展历史可以追溯到20世纪90年代初,随着互联网的快速发展和信息量的急剧增加,人们开始感受到了获取和管理信息的挑战。这些阶段展示了搜索引擎在技术和商业模式上的不断演进,以满足用户对信息获取的不断增长的需求。

随便推点

控制对象的特性_控制对象特性-程序员宅基地

文章浏览阅读990次。对象特性是指控制对象的输出参数和输入参数之间的相互作用规律。放大系数K描述控制对象特性的静态特性参数。它的意义是:输出量的变化量和输入量的变化量之比。时间常数T当输入量发生变化后,所引起输出量变化的快慢。(动态参数) ..._控制对象特性

FRP搭建内网穿透(亲测有效)_locyanfrp-程序员宅基地

文章浏览阅读5.7w次,点赞50次,收藏276次。FRP搭建内网穿透1.概述:frp可以通过有公网IP的的服务器将内网的主机暴露给互联网,从而实现通过外网能直接访问到内网主机;frp有服务端和客户端,服务端需要装在有公网ip的服务器上,客户端装在内网主机上。2.简单的图解:3.准备工作:1.一个域名(www.test.xyz)2.一台有公网IP的服务器(阿里云、腾讯云等都行)3.一台内网主机4.下载frp,选择适合的版本下载解压如下:我这里服务器端和客户端都放在了/usr/local/frp/目录下4.执行命令# 服务器端给执_locyanfrp

UVA 12534 - Binary Matrix 2 (网络流‘最小费用最大流’ZKW)_uva12534-程序员宅基地

文章浏览阅读687次。题目:http://acm.hust.edu.cn/vjudge/contest/view.action?cid=93745#problem/A题意:给出r*c的01矩阵,可以翻转格子使得0表成1,1变成0,求出最小的步数使得每一行中1的个数相等,每一列中1的个数相等。思路:网络流。容量可以保证每一行和每一列的1的个数相等,费用可以算出最小步数。行向列建边,如果该格子是_uva12534

免费SSL证书_csdn alphassl免费申请-程序员宅基地

文章浏览阅读504次。1、Let's Encrypt 90天,支持泛域名2、Buypass:https://www.buypass.com/ssl/resources/go-ssl-technical-specification6个月,单域名3、AlwaysOnSLL:https://alwaysonssl.com/ 1年,单域名 可参考蜗牛(wn789)4、TrustAsia5、Alpha..._csdn alphassl免费申请

测试算法的性能(以选择排序为例)_算法性能测试-程序员宅基地

文章浏览阅读1.6k次。测试算法的性能 很多时候我们需要对算法的性能进行测试,最简单的方式是看算法在特定的数据集上的执行时间,简单的测试算法性能的函数实现见testSort()。【思想】:用clock_t计算某排序算法所需的时间,(endTime - startTime)/ CLOCKS_PER_SEC来表示执行了多少秒。【关于宏CLOCKS_PER_SEC】:以下摘自百度百科,“CLOCKS_PE_算法性能测试

Lane Detection_lanedetectionlite-程序员宅基地

文章浏览阅读1.2k次。fromhttps://towardsdatascience.com/finding-lane-lines-simple-pipeline-for-lane-detection-d02b62e7572bIdentifying lanes of the road is very common task that human driver performs. This is important ..._lanedetectionlite